Chiplet 封装技术

核心技术优势

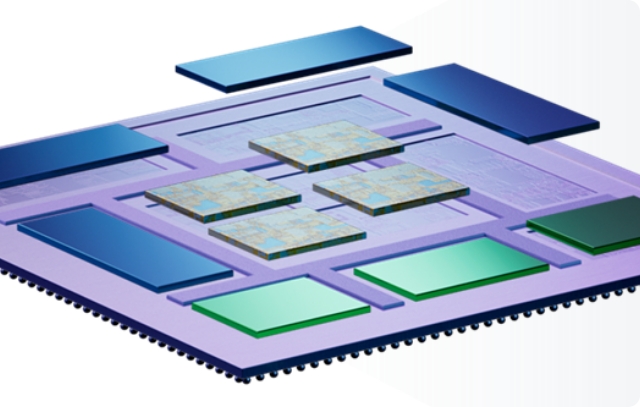

Chiplet 封装技术通过将多个异构芯粒(如计算芯粒、存储芯粒、IO 芯粒)集成在单一封装内,实现了 “模块化造芯” 的创新模式,其性能与成本平衡优势显著。与传统单芯片 SoC 相比,Chiplet 方案的设计周期缩短 50% 以上,7nm 工艺的 AI 芯片采用 Chiplet 后,流片成本降低 30% - 40%,这是因为单个芯粒的良率远高于全尺寸芯片 —— 当某一功能模块出现缺陷时,只需替换对应芯粒而非整片报废。台积电测试数据显示,16nm 工艺的 Chiplet 封装良率达 92%,较同规格 SoC(75%)提升 23%。

在性能扩展方面,Chiplet 技术展现出独特优势。通过先进互联技术(如硅中介层、混合键合),芯粒间的信号传输延迟可控制在 1ns 以内,带宽达 1TB/s,较传统 PCB 互联(延迟 10ns、带宽 10GB/s)提升 100 倍。某 AI 芯片企业采用 8 个计算 Chiplet 的堆叠方案,算力达 400TOPS,较单芯片方案(200TOPS)提升 1 倍,且功耗密度降低 20%,解决了大芯片的散热难题。

此外,Chiplet 的异构集成能力突破了材料限制。可将不同工艺节点(如 7nm 计算芯粒 + 28nm IO 芯粒)、不同材料体系(如 Si 计算芯粒 + SiC 功率芯粒)的模块集成,某车规级 MCU 采用 Chiplet 后,逻辑计算部分用 14nm 工艺提升性能,电源管理部分用 40nm 工艺保证可靠性,整体成本降低 25%,同时满足 - 40℃至 125℃的宽温需求。

关键突破

近年来,Chiplet 互联技术取得突破性进展。混合键合(Hybrid Bonding)技术将铜 - 铜直接键合的间距缩小至 1μm,较传统 solder bump(50μm)提升 50 倍,互联密度达 10 万个 /mm²。国内某研究机构开发的混合键合工艺,键合强度达 20MPa,良品率 98%,通过 1000 次温度循环测试后无脱键现象,满足车规级可靠性要求。

在标准化方面,UCIe(Universal Chiplet Interconnect Express)协议的推出统一了 Chiplet 互联接口,支持不同厂商芯粒的互操作性。基于该协议的测试芯片显示,AMD 的计算 Chiplet 与三星的存储 Chiplet 互联时,性能损失仅 3%,较非标准化方案(15%)提升 80%,大幅降低了跨厂商合作的技术门槛。

仿真工具的进步加速了 Chiplet 设计流程。新一代多物理场仿真软件可同时模拟芯粒间的电信号、热分布和机械应力,仿真误差控制在 5% 以内,较传统工具(15%)提升 67%。某设计公司采用该工具后,Chiplet 封装的热仿真时间从 72 小时缩短至 12 小时,设计迭代效率提升 5 倍。

行业应用

在高性能计算领域,Chiplet 技术成为算力提升的核心方案。AMD MI300X 采用 13 个 Chiplet(1 个 IO die+12 个计算 die),HBM 容量达 192GB,较上一代 MI250(128GB)提升 50%,AI 算力达 5.3PFLOPS,在大模型训练中,训练周期缩短 30%。英特尔至强处理器通过 Chiplet 集成 FPGA 芯粒,可灵活加速特定算法,某云计算厂商部署后,数据库查询效率提升 40%,同时能耗降低 15%。

智能手机芯片通过 Chiplet 实现功能升级。联发科天玑 9300 采用 “1 个超大核 + 3 个大核 + 4 个小核” 的 Chiplet 架构,其中超大核用 4nm 工艺,小核用 7nm 工艺,较全 4nm SoC 成本降低 20%,同时 CPU 多核性能提升 15%。某旗舰机型搭载该芯片后,安兔兔跑分突破 220 万分,较上一代提升 18%,且待机功耗降低 10%。

车规芯片领域因 Chiplet 技术提升可靠性。恩智浦的 S32Z/E 系列车规处理器采用 Chiplet 设计,将安全岛模块(负责自动驾驶安全监控)与主计算模块分离,安全岛模块通过 ASIL D 认证,主计算模块达 ASIL B,既满足功能安全要求,又降低了整体设计复杂度。某自动驾驶域控制器采用该芯片后,系统故障间隔时间(MTBF)达 10000 小时,较传统方案提升 1 倍。

现存挑战

Chiplet 技术的发展面临互联瓶颈。混合键合技术的量产良率仅 70%(实验室可达 90%),主要受限于表面平整度控制 —— 键合界面的粗糙度需低于 0.5nm,而量产中实际可达 0.8nm,导致部分键合点接触电阻增大 10 倍。硅中介层的成本居高不下,300mm 硅中介层的加工成本达 500 美元 / 片,是普通封装基板的 10 倍,推高了 Chiplet 的整体成本。

标准化体系尚未完全统一。除 UCIe 外,还有 CCIX、Gen-Z 等多种互联协议,不同协议间的转换效率损失达 15% - 20%。某跨厂商合作项目中,因采用不同协议的 Chiplet,互联带宽从理论 1TB/s 降至 800GB/s,影响了性能发挥。此外,芯粒的测试标准缺失,不同厂商的芯粒兼容性验证周期长达 3 个月,延长了产品上市时间。

设计复杂度是另一大挑战。Chiplet 的信号完整性(SI)和电源完整性(PI)设计需考虑多芯粒协同,仿真工作量增加 3 倍以上。某设计公司的 7nm Chiplet 项目中,因忽略芯粒间的同步时钟偏差(达 50ps),导致初期样品的运算错误率达 0.1%,通过优化时钟树网络后才降至 0.001%,额外投入研发成本 100 万美元。

Chiplet 封装技术作为延续摩尔定律的重要路径,正在重塑芯片设计范式。随着混合键合成本下降(预计 2025 年降至 200 美元 / 片)和 UCIe 协议普及,预计 2027 年全球 Chiplet 市场规模将突破 300 亿美元,在 AI 芯片、车规 MCU 等领域的渗透率超 50%。未来,Chiplet 将向三维堆叠(3D IC)方向发展,通过 TSV(硅通孔)实现芯粒的垂直互联,进一步提升集成密度,为 “万亿晶体管时代” 提供可行的技术方案。